Pinball info

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

WIP: Creating a generic replacement for RRIOT 6530-0xx and 6532

- Thread starter fhw72

- Start date

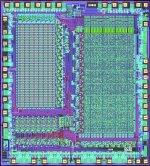

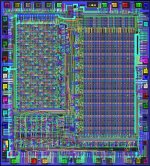

Very nice project  I just love die shots they're so cool.

I just love die shots they're so cool.

Are you planning to implement in a FPGA?

Are you planning to implement in a FPGA?

Yes... we'll use an FPGA for implementation. The prototype will be realized using another project I did in the past:

MockA65xx - DILboard

For copyright reasons it might be necessary that the user has to upload the ROM content... but we'll see.

The plan is/was to incl. as many ROMs as possible and provide a possibility to switch between ROM versions.

Similar to this project:

PLAdvanced+

First thing is getting one variant of the 6530-0xx running... and there are quite a few variants known:

6530-0xx variants

MockA65xx - DILboard

For copyright reasons it might be necessary that the user has to upload the ROM content... but we'll see.

The plan is/was to incl. as many ROMs as possible and provide a possibility to switch between ROM versions.

Similar to this project:

PLAdvanced+

First thing is getting one variant of the 6530-0xx running... and there are quite a few variants known:

6530-0xx variants

Last edited:

wow that in incredible I had no idea there was even enough data from a die image to reverse engineer? Are there not many different layers? Some of which will be hidden?

Or is it more just reading the data sheet and emulating the functionality of the chip and matching it’s pinout?

Or is it more just reading the data sheet and emulating the functionality of the chip and matching it’s pinout?

wow that in incredible I had no idea there was even enough data from a die image to reverse engineer? Are there not many different layers? Some of which will be hidden?

Or is it more just reading the data sheet and emulating the functionality of the chip and matching it’s pinout?

Many just take the datasheet and try to mimic the *specified* functionality which regularly leaves out undocumented features or bugs.

That's NOT our approach: We aim for an (almost) 100% emulation by understanding the actual inner workings of the chip and

converting it to a HDL (Verilog in this case).

The number of relevant layers on these old chips is quite limited. Usually only 3 are needed: Metal, Polysilicon and Diffusion.

Everything else is helpful but not necessary. By carefully distinguishing these layers and redrawing them it's quite easy to obtain

the transistor netlist. Though this can be a quite time consuming task.

Sometimes the Metal layer hides details... in this case we have to etch away the metal layer to see the layers below.

D

Deleted member 2463

Love to see stuff like this and whilst those IC’s were state of the art back in the day we are lucky that compared to today’s IC’s they were very simple.

Who owns the copyright for this chip?

Sent from my iPhone using Tapatalk Pro

Who owns the copyright for this chip?

Sent from my iPhone using Tapatalk Pro